Category: General

2014-Q4 日劇學院賞

別了,政桓同學

2015-0225

fold@home 似乎讓我漸漸的著迷。

所以也參加了滄者極限的贊助活動,進了一張Nvidia GTX970 希望對重大的疾病探索,與台灣隊的排名提升有一定的幫助。

[轉貼] IPMI

http://blog.csdn.net/dog250/article/details/6136202

ipmi-智能平台管理接口是一个标准,它的实现核心是一个芯片,叫做BMC,它独立于计算机常规部件比如cpu,内存等等然而却真真的存在于主板或者刀片上。基于BMC使用ipmi,你可以不依赖操作系统对机器进行监控或者管理,甚至远程管理,管理的范畴甚至可以是电源操作,比如开机,关机,重启等,比运行于操作系统的SNMP软件要灵活很多,之所以管理的范畴如此之宽就在于BMC芯片的独立性,它独自存在于板卡上,独立供电,只要接通电源它就被供电,甚至可以使用单独的电池给与供电,这样的话,致命的停电(设想ups已损坏)之类的问题都可以被监控到。当机器还没有开启的时候,也就是cpu还没有开始运行的时候,此时假设电源已经接上了,还没有按下开机键,这个时候,BMC芯片已经开始运行了,它可以从网络接收“命令”,然后帮助管理员打开机器,这样管理员就可以在一个地方同时控制N多机器了而不必再往返于各个机房,管理员也可以通过ipmi远程查看任何机器的cpu温度之类的信息,然后根据信息反馈采取相应的动作或者什么也不做。 Continue reading [轉貼] IPMI

士東婦幼資訊

http://blog.yam.com/recco/article/73965462

Fold@home Linux GPU

http://www.overclock.net/t/1506137/ubuntu-f-h-installation-for-ubuntu-gpu-cpu

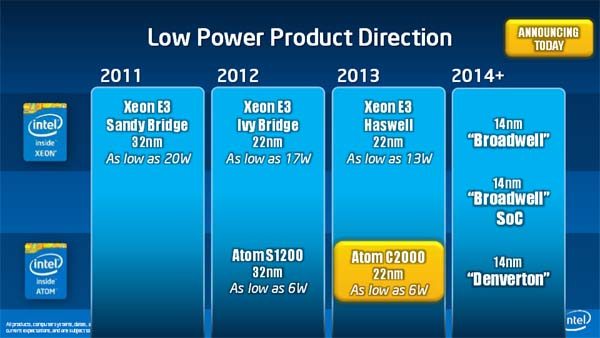

Intel Broadwell DE

http://www.cpu-world.com/news_2014/2014061301_Some_details_of_Intel_Broadwell-DE_processors.html

The latter systems on a chip will be a part of Grangeville platform for storage and communications, as well as for microservers markets. The SoCs, codenamed “Broadwell-DE”, will integrate not only “Broadwell” CPU cores and a memory controller, but also an I/O block and Platform Controller Hub (PCH) logic. We do not have verified information about the core count, however a SoC block diagram, that we have seen, shows 8 cores. Each core has 1.5 MB of L3 cache, as a result an 8-core processor should have 12 MB of L3 cache. The cores support most of Broadwell technologies, including Hyper-Threading, Turbo Boost, VT-x and VT-d virtualization, and Trusted Execution. Broadwell-DE parts for storage and communications also support QuickData technology 3.3. The processors have AES and AVX2 extensions enabled. New features in SoCs are Processor Trace (can capture details of code execution), supervisor mode access prevention, and extensions to ADC instruction.

Broadwell-DE chips incorporate a dual-channel memory controller, that supports DDR3L memory with data rates up to 1600 MHz, and DDR4 memory with data rates up to 2133 MHz, and up to 2400 MHz on some SKUs. Each channel supports up to 2 DIMMs, which allows the SoC to address up to 128 GB of RAM when 32GB DIMMs are used.

The I/O block includes 10 Gigabit Ethernet controller and 24 lanes of PCI-Express 3.0 interface. Furthermore, the on-chip PCH has 8 lanes of PCI-Express 2.0 interface, and 1Gb Ethernet controller. The PCH also provides 6 ports of SATA 6GB/s, 4 ports of USB 3.0 and 4 ports of USB 2.0.

The SoCs will be manufactured in a BGA package.